The

front-end electronics

The

readout of the HMPID modules is organized according to a parallel/serial

architecture and is based on the VLSI GASSIPLEX chip, specifically developed to

enable the determination of the hit coordinates by centroid measurement. It is

characterized by a filtering scheme designed to cope with the shape of the

signal delivered by MWPCs and by a long peaking time (1.2 ms)

suitable for an external event trigger. An average noise of 1000 e-

has been measured on detector.

The

16-channel preamplifier/shaper GASSIPLEX chips, uniformly distributed on the

back side of the cathode pad planes, are operated in analog multiplexed ‘Track

and Hold’ mode, storing the electric charge into internal capacitors in

coincidence with the arrival of a trigger signal.

Each

HMPID module is divided into two halves, in turn segmented into 24 rows of 10

daisy-chained 3-GASSIPLEX (3-G) cards. Each 3-G card performs a serial readout

of 48 pads at 10 MHz multiplexing frequency and the corresponding signals are

sequentially sent to a commercial 12-bit ADC (for analog-to-digital conversion)

and to the DILOGIC, an ASIC chip specifically

designed for zero-suppression. For Pb–Pb central events, an occupancy of 15%

has been estimated, corresponding to a total readout time of less than 200 ms.

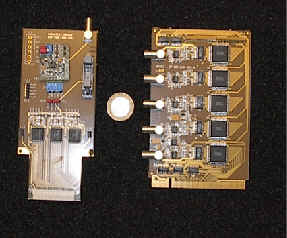

The FEE cards: GASSIPLEX (left) and DILOGIC (right)

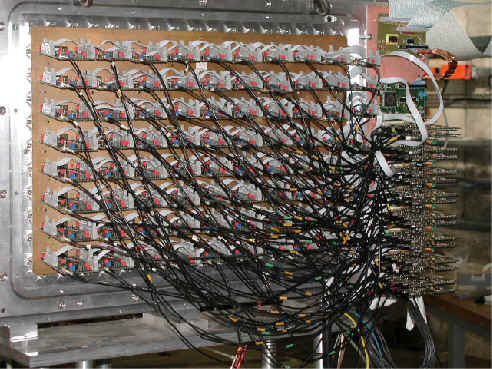

Proto-3 fully equipped with the final FEE